# The United States of America

Has received an application for a patent for a new and useful invention. The title and description of the invention are enclosed. The requirements of law have been complied with, and it has been determined that a patent on the invention shall be granted under the law.

Therefore, this

# **United States Patent**

*Grants to the person(s) having title to this* patent the right to exclude others from making, using, offering for sale, or selling the invention throughout the United States of America or importing the invention into the United States of America, and if the invention is a process, of the right to exclude others from using, offering for sale or selling throughout the United States of America, or importing into the United States of America, products made by that process, for the term set forth in 35 U.S.C. 154(a)(2) or (c)(1), subject to the payment of maintenance fees as provided by 35 U.S.C. 41(b). See the Maintenance Fee Notice on the inside of the cover.

Michelle K. Lee

Director of the United States Patent and Trademark Office

### US009018662B2

# (12) United States Patent Chung et al.

### (10) **Patent No.:**

## US 9,018,662 B2

### (45) Date of Patent:

### Apr. 28, 2015

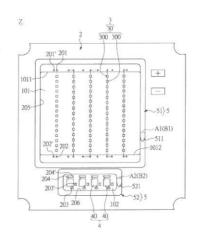

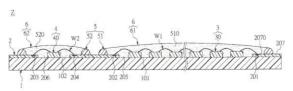

### (54) MULTICHIP PACKAGE STRUCTURE

# (71) Applicant: Paragon Semiconductor Lighting Technology Co., Ltd., New Taipei (TW)

- (72) Inventors: Chia-Tin Chung, Miaoli County (TW); Shih-Neng Tai, Taoyuan County (TW)

- (73) Assignee: Paragon Semiconductor Lighting Technology Co., Ltd., New Taipe (TW)

- (\*) Notice: Subject to any disclaimer, the term of this patent is extended or adjusted under 35 U.S.C. 154(b) by 0 days.

- (21) Appl. No.: 14/076,489

- (22) Filed: Nov. 11, 2013

- (65) **Prior Publication Data**US 2015/0061513 A1 Mar. 5, 2015

- (30) Foreign Application Priority Data

Aug. 30, 2013 (TW) ...... 102131265 A

- (51) Int. Cl. H01L 33/50 (2010.01) H01L 25/075 (2006.01) H05B 33/08 (2006.01)

- (52) U.S. Cl. CPC ....... *H01L 25/0753* (2013.01); *H05B 33/0806*

### (56)

# References Cited U.S. PATENT DOCUMENTS

| 6,410,940    | B1 * | 6/2002  | Jiang et al   | 257/82 |

|--------------|------|---------|---------------|--------|

| 6,498,355    | B1 * | 12/2002 | Harrah et al  | 257/99 |

| 6,661,030    | B2 * | 12/2003 | Komoto et al  | 257/98 |

| 8,217,404    | B2 * | 7/2012  | Wu et al      | 257/88 |

| 8,791,471    | B2 * | 7/2014  | Leung         | 257/88 |

| 2011/0193109 | A1*  | 8/2011  | Loh           | 257/89 |

| 2012/0132938 | A1*  | 5/2012  | Komatsu et al | 257/89 |

<sup>\*</sup> cited by examiner

Primary Examiner — Tung X Le

(74) Attorney, Agent, or Firm — Li&Cai Intellectual Property (USA) Office

### (57) ABSTRACT

A multichip package structure includes a metal substrate, a circuit substrate and a light-emitting module. The metal substrate has a first mirror plane area and a second mirror plane area. The circuit substrate is disposed on the metal substrate. The circuit substrate includes a plurality of first conductive pads, a plurality of second conductive pads, a first passing opening for exposing the first mirror plane area, and a second passing opening for exposing the second mirror plane area. The light-emitting module includes a plurality of light-emitting units disposed on the first mirror plane area. Each lightemitting unit includes a plurality of LED chips disposed on the first mirror plane area. The LED chips of each lightemitting unit are electrically connected between the first conductive pad and the second conductive pad in series. Thus, the heat-dissipating efficiency and the light-emitting effect of the multichip package structure can be increased.

### 13 Claims, 8 Drawing Sheets